〒224-0041 神奈川県横浜市都筑区仲町台1-3-7

◆電車でお越しの場合

横浜市営地下鉄ブルーライン 仲町台駅より徒歩1分

◆お車でお越しの場合

第三京浜 都筑インターより5分

1. 概要

① Verilog-HDL によるシリアルインターフェースの作成を行う。

2. 動作仕様

① 送信データは16bit データ×4 セット送信を行う。

② 送信データはプリセットの他、モジュール外部から書き換え可能にする。

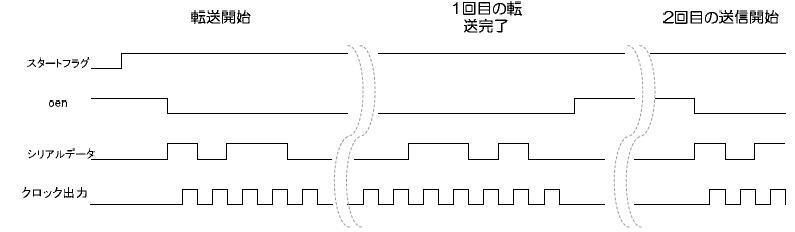

③ 送信タイミングは以下の通り。以下の送信を×4 セット送信を行う。

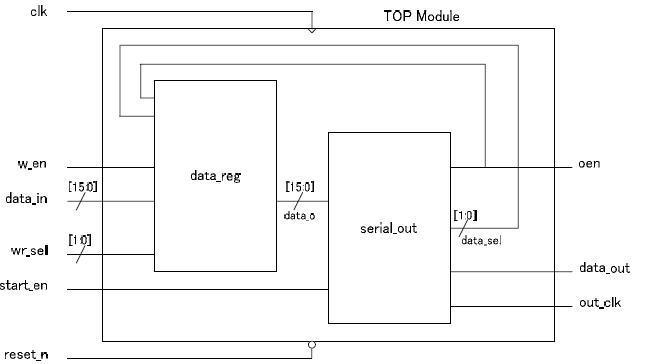

bブロック図

3. ソース記述

Data_reg ブロック

・シリアルデータの保持、書き換えを行う。

・シリアル転送回数より、次に送信するシリアルデータのセレクトを行う。

data_reg ブロックソース

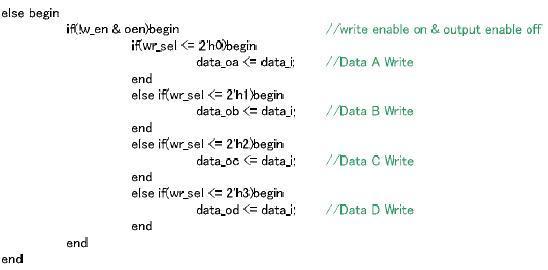

・書き換えデータセレクト

データレジスターブロックへのデータ書き込み条件は、シリアル転送を行っていない時(oen = H 時)、w_en がL 時で書き込み可。

wr_sel より何回目の転送データを書き換えるかセレクトする。

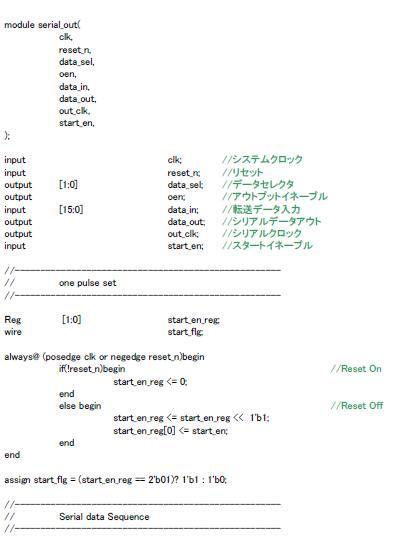

serial_out ブロック

・Start フラグを受信後動作開始。

・16bit データをMSB Fast でシリアルデータを4 回送信行う。

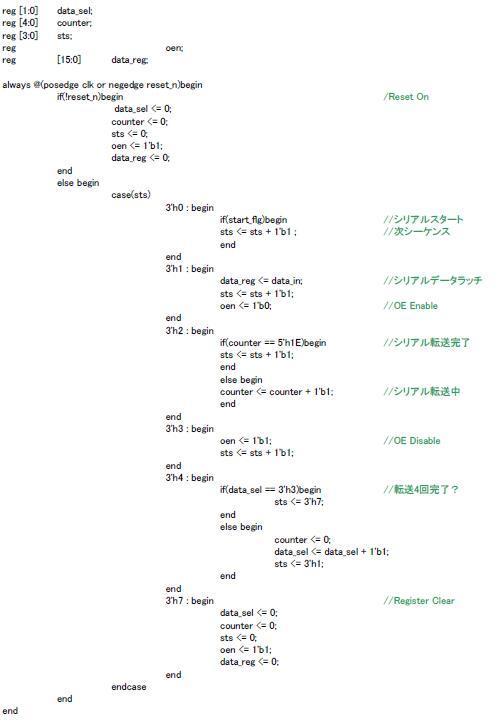

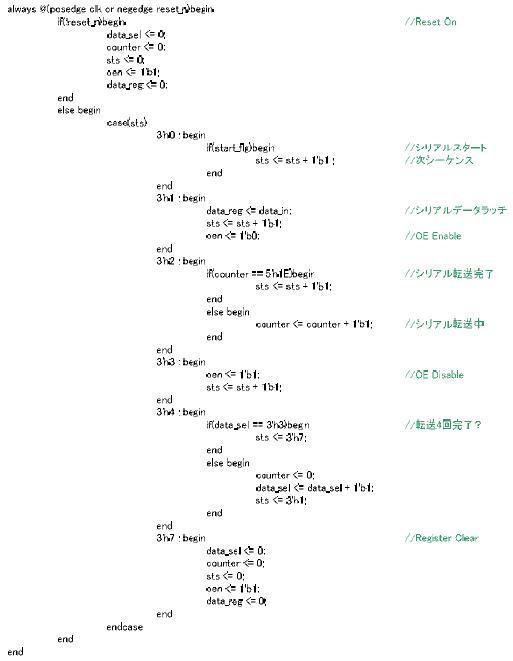

Serial_out ブロックソース

・シーケンス部ソース

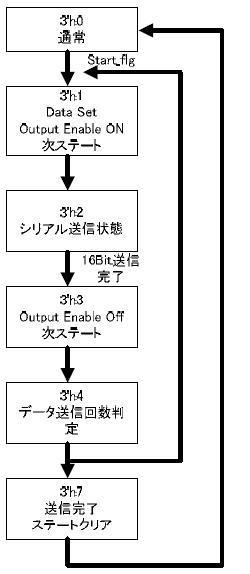

各シーケンスの状態遷移が以下の通り

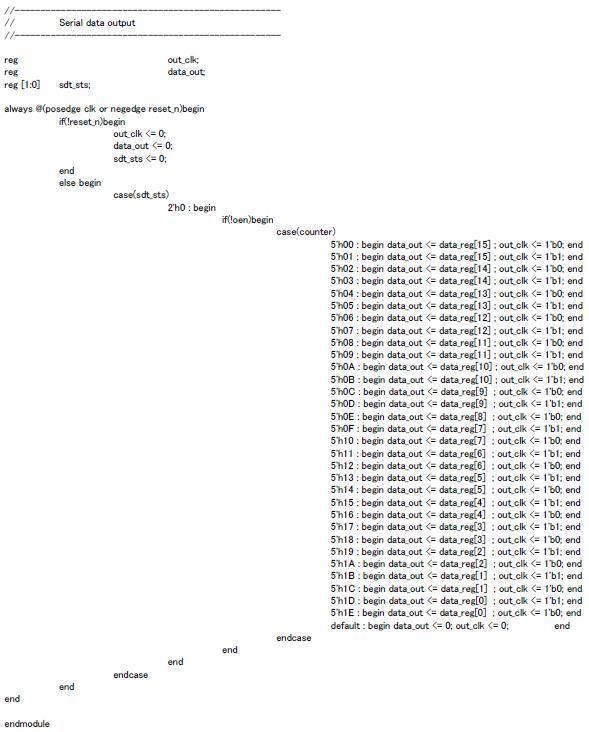

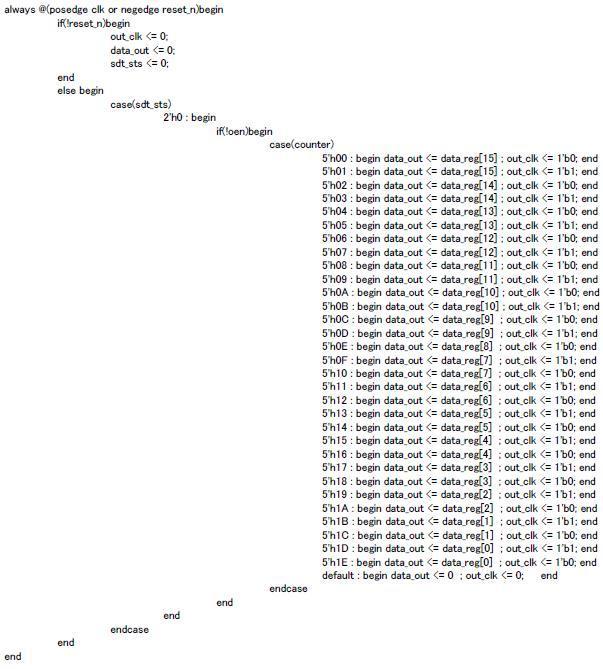

・データ送信部ソース

シリアル送信状態シーケンスに回すカウンタの値に応じて動作を行う。

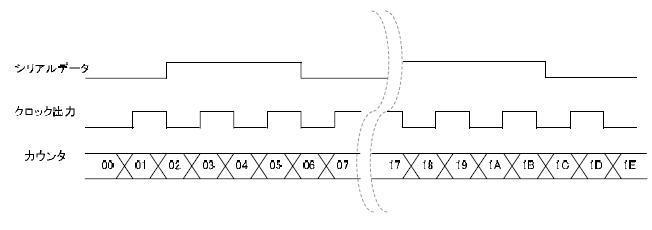

タイミングチャートは以下の通り。

4. シミュレーション

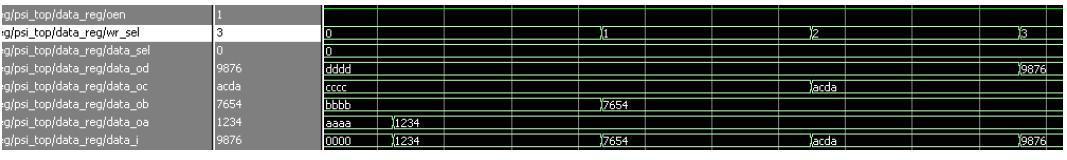

Data_reg ブロックシミュレーション

テストベンチ上からWr_sel、data_i より信号を与え、シリアルデータが書き変わること事を確認した。

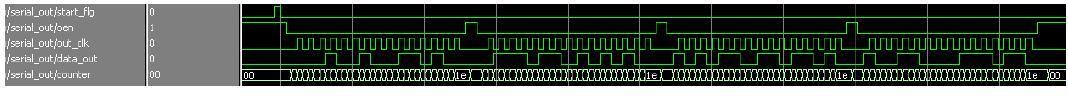

・serial out ブロックシミュレーション

テストベンチ上からserial out ブロックにスタートフラグを与え、シリアルデータが送信出来ている事を確認した。

お問合せ・ご相談はこちら

弊社はアナログおよびデジタルの電子回路設計でお悩みのお客様に、最適なハードウエアデザイン・ソフトウエアデザインをご提供します。

高周波アナログ回路設計と高集積ロジック信号処理の両方に強みを持っております。

また、環境に配慮した省電力、省資源で電子機器のシステム化をお手伝いします。

アナログデジタル電子回路設計センター

住所

〒224-0041

神奈川県横浜市都筑区仲町台1-3-7

アクセス

◆電車でお越しの場合

横浜市営地下鉄ブルーライン 仲町台駅より徒歩1分

◆お車でお越しの場合

第三京浜 都筑インターより5分