〒224-0041 神奈川県横浜市都筑区仲町台1-3-7

◆電車でお越しの場合

横浜市営地下鉄ブルーライン 仲町台駅より徒歩1分

◆お車でお越しの場合

第三京浜 都筑インターより5分

ER-1005A 基準信号発生器

この製品の購入についてのお問い合わせは

| 販売元 株式会社エディックシステムズ 〒224-0041 神奈川県横浜市都筑区仲町台1丁目3-7 TEL:045-949-0081 FAX:045-949-6881 E-Mail:info@edic-systems.co.jp |

までお願いいたします。

EA-1001A 信号切替バッファーアンプ

本器は、10MHz入力部AとBを持ち、いずれかの信号を16系統へ分配することができます。

基準信号発生器ER-1005Aのステータス情報を受けて、入力Aと入力Bの10MHz信号の信頼性が高い方の入力を切替えて出力することができます。前面パネルのスイッチを操作することでマニュアルで入力を選択することもできます。

この製品の購入についてのお問い合わせは

| 販売元 株式会社エディックシステムズ 〒224-0041 神奈川県横浜市都筑区仲町台1丁目3-7 TEL:045-949-0081 FAX:045-949-6881 E-Mail:info@edic-systems.co.jp |

までお願いいたします。

ER-1003A 基準信号発生器

ルビジウム発振器を基準としている10MHzの信号発生器です。

従来のルビジウム基準信号発生器に比較して、小型、軽量となっています。

バッテリを搭載し、可搬性に優れ、各種の電子計測器の外部基準周波数の用途に最適です。

この製品の購入についてのお問い合わせは

| 販売元 株式会社エディックシステムズ 〒224-0041 神奈川県横浜市都筑区仲町台1丁目3-7 TEL:045-949-0081 FAX:045-949-6881 E-Mail:info@edic-systems.co.jp |

までお願いいたします。

新技術創出交流会の出展模様

2015年10月27日にパレスホテル立川で開催された「新技術創出交流会」に株式会社エディックシステムズも出展いたしました。

当日は多くのお客様に弊社製品に関心を寄せていただくことが出来ました。

お立ち寄りいただいた皆様、誠にありがとうございました。

新技術創出交流会に出展します

株式会社エディックシステムズは、10月27日 立川パレスホテルにて行われます「新技術創出交流会」に出展いたします。

弊社ブースでは、「920MHz帯特定小電力USB無線モジュール」、「920MHz帯特定省電力無線モジュール」、「ホワイトスペースセンシングユニット」を展示いたします。

ご興味のある方、ご来場の際は是非弊社ブースにお立ち寄りください。

新技術創出交流会の概要

| 会期 | 平成27年10月27日 (火) 11:00〜16:40 |

| 場所 | 東京都立川市曙町2-40-15 パレスホテル立川4階 ローズルーム (JR立川駅北口より徒歩3分) |

| ブースNo. | 77 |

| 主催 | 公益財団法人東京都中小企業振興公社 |

| URL | http://www.keieiryoku.jp/topics/detail.php?id=811 |

入場無料、予約不要

ワイヤレスジャパン2015に出展

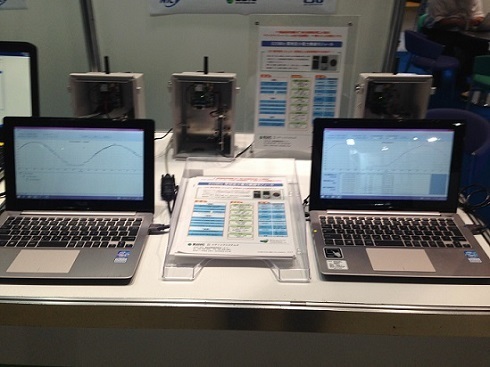

2015年5月27日(水)から5月29日(金)まで東京ビッグサイトで開催された「ワイヤレスジャパン2015」にWi-SUNアライアンスContributor Memberとして出展いたしました。

デモンストレーションを国立研究開発法人情報通信研究機構、株式会社アイ・エス・ビーと合同で実施し、多くの方々にご紹介できました。

特にIEEE802.15.4e Low Energy Super Frame オプションを搭載したモジュールを唯一展示し、M2M(マシン・トゥー・マシン)データ転送において必要となる低消費電力性をお知らせすることが出来ました。

お立ち寄りいただいた皆様、誠にありがとうございました。

昨年に引き続き今年も、株式会社エディックシステムズはWi-SUN アライアンス Contributor Memberとして「ワイヤレスジャパン2014」に参加し、新たに開発した920MHz帯特定小電力モジュールのUSBタイプを発表いたしました。

デモンストレーションを独立行政法人情報通信研究機構、株式会社アイ・エス・ビーと合同で実施し、多くのお客様に関心を寄せていただくことができたことを、社員一同大変嬉しく思っております。

当社はWi-SUN アライアンス・インターオペラビリティテストにおいてIEEE802.15.4g/4e規格をベースとする物理層・データリンク層の相互接続試験を行い確認した無線通信プロトコルを実装した920MHz帯での技術基準適合証明取得済みの無線モジュールを用い、スマートハウス等において要件の一つと考えられている6LoWPANおよびIPv6といった上位プロトコルの実装が可能な拡張性を有する無線モジュールを展示いたしました。

・要旨

株式会社エディックシステムズはWi-SUN アライアンス Contributor Memberとして「ワイヤレスジャパン2013」に参加し、920MHz帯特定小電力モジュール及び無線機の出展とデモンストレーションを独立行政法人情報通信研究機構、株式会社ACCESS、株式会社村田製作所と合同で実施します。

当社はWi-SUN アライアンス・インターオペラビリティテストにおいてIEEE802.15.4g/4e規格をベースとする物理層・データリンク層の相互接続試験を行い確認した無線通信プロトコルを実装した920MHz帯での技術基準適合証明取得済みの無線モジュールを用い、スマートハウス等において要件の一つと考えられている6LoWPANおよびIPv6といった上位プロトコルの実装が可能な拡張性を有する無線モジュールを展示しております。

・ワイヤレスジャパンの概要

会期: 2013年5月29日(水) 〜5月31日(金)

場所: 東京ビッグサイト 西ホール

URL: http://www8.ric.co.jp/expo/wj/

Wi-SUN Alliance ブースNo.: SM-10

▼概要

ARIB STD-T108に準拠した920MHz帯の周

波数を利用した特定小電力モジュールを、情報

通信研究機構(NICT)様の技術移転許諾により製

品化致しました。専用LSIを製作し実装する事に

より、他社には無いより高度な短距離無線通信

システムを容易に構築する事が出来ます。

▼特長

・IEEE802.15.4g規格に準拠したPHY

・IEEE802.15.4e規格に準拠したMAC

・JJ300.10(方式A、C: Wi-SUN-IP)対応

・LESF(ローエナジースーパーフレームオプション)動作を専用LSIにより実現し、

FEC(15.4g準拠)機能実装

・小型軽量な無線モジュール

▼仕様

| 規格 | ARIB STD-T108 |

| 通信方式 | 単向通信方式, 単信方式 |

| 定格出力 | 20mW |

| 電波形式 | F1D |

| 周波数 | 920.6MHz〜928.0MHz |

| 変調方式 | GFSK |

| 変調速度 | 50kbps/100kbps/200kbps |

| 誤り訂正機能 | Viterbi |

| インターフェース | シリアル通信インターフェース |

| 電源電圧 | +3.3V±0.3 |

| 消費電流(Typ) | 送信時54mA |

| 使用温度 | -10℃〜+60℃ |

| 外形寸法 | 20(W)×40(D)×3(H)mm |

| 重量 | 約4.0g |

▼ FPGA搭載 開発用無線モジュール

機能拡張等による回路構成変更、評価確認用として、

FPGA搭載の無線モジュールも準備しております。

インターフェースボートと合わせる事で、より高度な

開発環境をご提供致します。

▼その他

・チップアンテナ対応可能

・TELEC技術基準適合証明取得済み

・Wi-SUNアライアンス インターオペラビリィティテストへ参加し確認済み

・到達距離実験実績あり

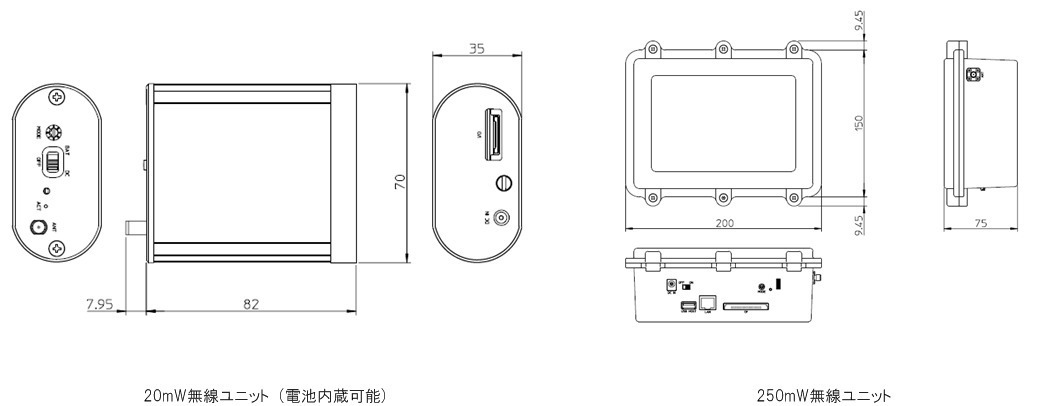

▼概要

弊社920MHz帯特定小電力モジュールを搭載

した無線ユニットとして、情報通信研究機構(NICT)

様の技術移転許諾により製品化致しました。

20mWの無線ユニットだけではなく、無線電波の

到達距離等に応じて、250mWの無線ユニットも

用意し、他社には無いより高度な短距離無線通信

システムを容易に構築する事が出来ます。

▼外形寸法

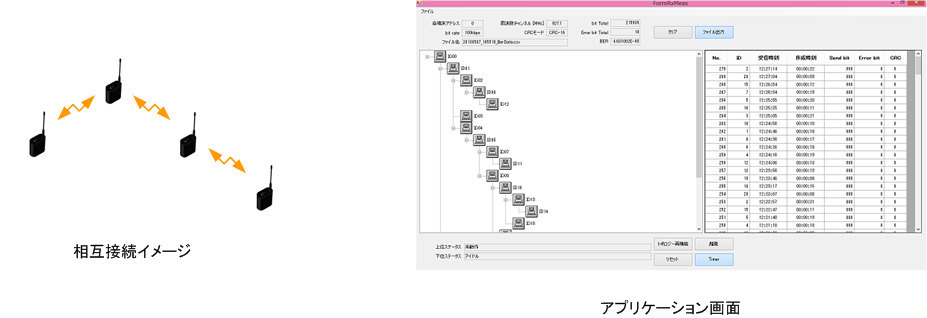

▼システム運用例

920MHz帯の周波数を利用し、無線機器が相互通信をおこなうことにより、短距離無線通信システムを容易に構築することが出来ます。

▼その他

・20mW無線ユニット

電源電圧 +5.0V

(単三電池×3本でも動作可能)

電池内蔵可能

・250mW無線ユニット

電源電圧 +12.0V

・内蔵アンテナ対応可能

・TELEC技術基準適合証明取得済み

・Wi-SUNアライアンス インターオペラビリィティテストへ参加し確認済み

・到達距離実験実績あり

▼特長

・IEEE802.15.4e ローエナジースパーフレームオプション動作を実現

・内部タイマーによる時間管理で超低消費電力動作

・FEC(誤り訂正)、インターリーブ回路を実装

▼機能

・FEC (誤り訂正)機能あり ON/OFF選択可能

RSC encoder (recursive and systematic code)

NRNSC encoder (Non-recursive and Non-systematic code)

両方のエンコーダ・Viterbiデコーダに対応

・データホワイトニング ON/OFF選択可能

・インターリーブ ON/OFF選択可能

・プリアンブル長選択可能 (デフォルト6octed)

・CRC16(2octed)とCRC32(4octed)選択可能

・SFD設定機能搭載

・ADF7023-J接続ポート装備

・送受信バッファ内蔵

▼ PHY-MAC LSI 外観

▼諸元

・LQFPパッケージ

80pin 12.0mmx12.0mmx1.7mm

・リードピッチ 0.5mm

・電源電圧 +3.3V±0.3V

はじめ

LCR 回路において、平行して走る信号配線、伝送線路による波形反射やクロストークが発生し、波形乱れの現象がよく起こります。この波形乱れは、電気回路で山びこのような電気信号の跳ね返りなので、なるべく跳ね返らないような工夫をします。電気信号の反射やクロストークの影響を避けるために最も多用されている手法はダンピング抵抗です。

ダンピング抵抗とは

ダンピング抵抗(damping )とは、振動を減衰させるという意味で、電子回路において LC 共振を抑制でき、信号ノイズの低減、オーバーシュート・アンダーシュートを抑制なども可能となる抵抗です。抵抗値は数十Ω 程度です。

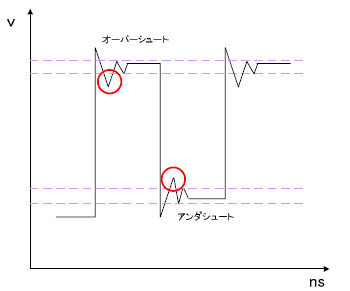

オーバーシュート/アンダシュートとは、矩形波の立ち上がり/立ち下がりの部分において、波形が定常値となる基線を超過する現象のことである。

下の波形はオーバーシュートとアンダシュートのイメージ図です。

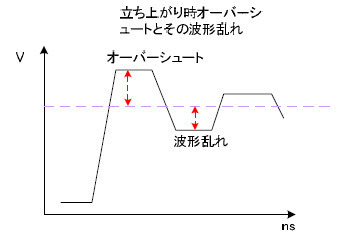

波形の乱れの影響

波形乱れとは、オーバシュートとその跳ね返りが主なものです。この跳ね返りが深く(大きく)なると、最終的には波形割れを生じます。波形乱れがあることによって回路に影響を及ぼす可能性があります。

・波形が歪む、ノイズが発生する。

・波形のタイミングがずれる。

・誤り動作が起こしやすい。

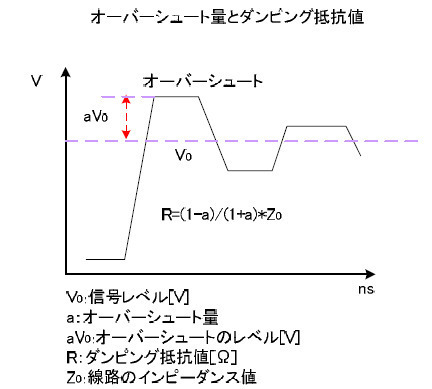

ダンピング抵抗値を決める

波形乱れ対策に最も多用されるダンピング抵抗は基本的に、ドライバの出力抵抗の値と線路の特性インピーダンスの値とを近づけるために利用するものです。この抵抗をドライバの出力に直列に挿入します。 一般的にドライバの出力抵抗は、線路の特性インピーダンスの1/3 になっています。

線路の特性インピーダンスを50Ω の場合、ドライバの出力抵抗は50÷3=17Ω です。

70Ω の線路の場合には、70÷3=23Ω です。

ダンピング抵抗値とオーバーシュート量、線路インピーダンスの関係

ダンピング抵抗の値は17Ω、23Ωがよく用いられますが、適当なダンピング抵抗値は波形の乱れをなるべく小さく収めるように選びます。

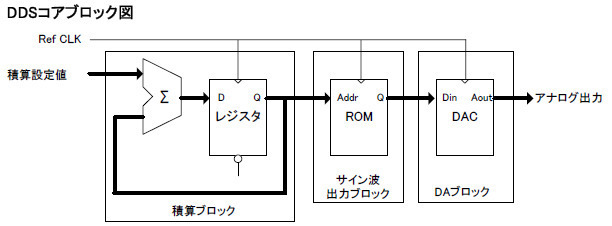

1. 概要

DDS の動作原理に関して記載をする。

2. DDS について

DDS(ダイレクト・デジタル・シンセシス)とは周波数、位相の可変が可能な信号発生器である。

3. DDS の動作原理

DDS は大きく分けてROM、加算回路、DAC で構成されている。動作原理、各ブロックの動作とブロック図を記載する。

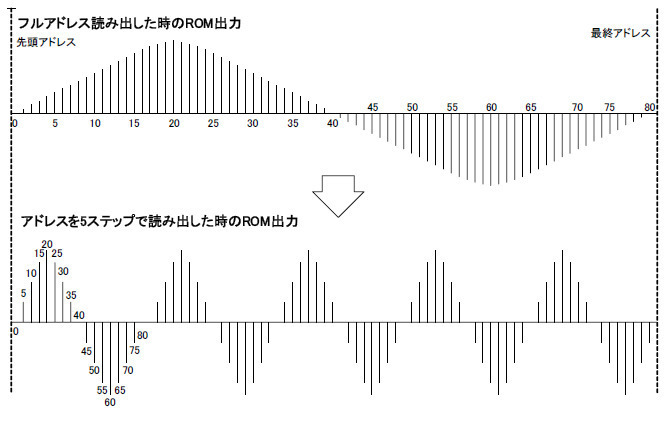

① ROM ブロック

DDS は1 サイクル分のサイン波データを格納したROM を持っており、先頭アドレスから最終アドレスまでを順次読み出す事で1 サイクル分のサイン波が出力される。

② 積算ブロック

積算ブロックの役割はROM のアドレス制御を行い出力周波数のコントロールを行う。

1 サイクル分の動作として、リファレンスクロックに同期し、積算設定値ステップで積算(積算設定値を5 とした場合0、5、10・・・)を行っていく。この積算結果がROM のアドレスとなる。

これが1 サイクル分の積算ブロックの動作となる。

以下の図は積算設定値を5 に設定し、ROM データを読み出した時の図である。ROM のアドレスを5 ステップでアクセスするため、出力周波数はROM をフルアドレスアクセスした場合と比較し5 倍の周波数となる。

DDS の出力周波数の設定はリファレンスクロックの速度、積算回路の積算設定値によって可変できる。DDS の出力周波数は以下の計算式から算出を行える。

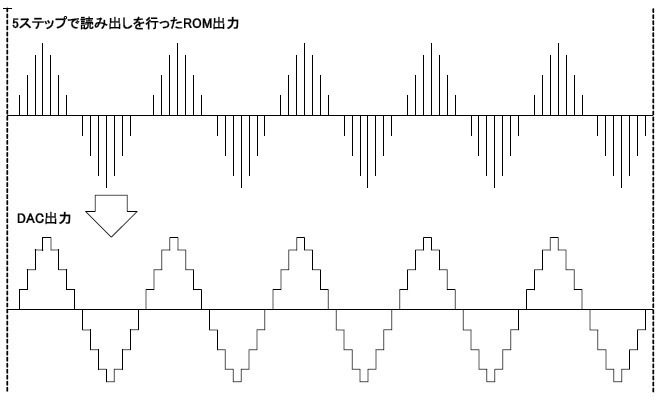

③ DA ブロック

DA ブロックではROM から出力されたデジタルデータ(振幅)のDA 変換を行っている。

その他の機能としてレジスタ等から出力ゲインを可変させる事も出来る。

1. 概要

FTDI/FT2232H はUSB2.0 から様々な通信方式に変換を行うデバイスである。今回はその

通信方式の一つであるHost Bus Emulation を用いた設計について記載する。

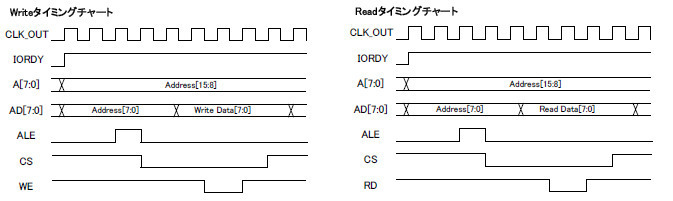

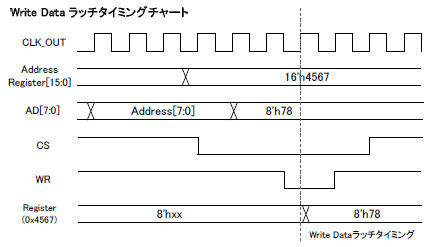

2. Host Bus Emulation について

Host Bus Emulation はアドレスバス16bit、データバス8bit を用いたパラレル送受信である。

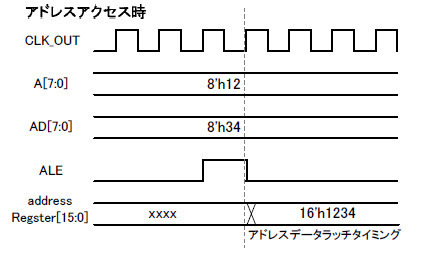

AD[7:0]はアドレスバスのLSB8bit、データバス8bit を共用で使用している。アドレスアクセス、

データバスアクセスの切り分けはALE、CS、WR、RD の信号によって制御される。

Write/Read 時のタイミングは以下の通り

3. 設計ポイント

AD[7:0]がアドレスバスのLSB、データバスと共用のため条件分岐による切り分けを行う必要がある。

アドレスアクセス時はアドレスレジスタ[15:0]への書き込み条件にALE のH レベルを検出でA[7:0]をアドレスレジスタのMSB[15:8]、AD[7:0]をアドレスレジスタのLSB[7:0]にラッチを行う。

データバスアクセス時の切り分けとして書き込み時はCS のL 検出と、WR のL 検出のアンド条件で指定されたアドレスへの書き込みを行う。

読み出し時は CS のL 検出と、RD のL 検出のアンド条件で指定されたアドレスから読み出しを行う。

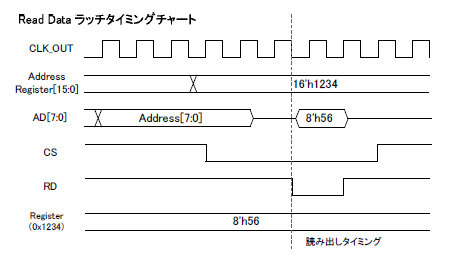

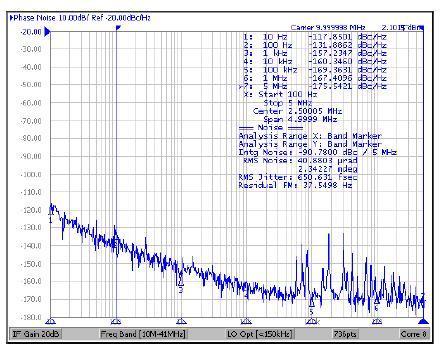

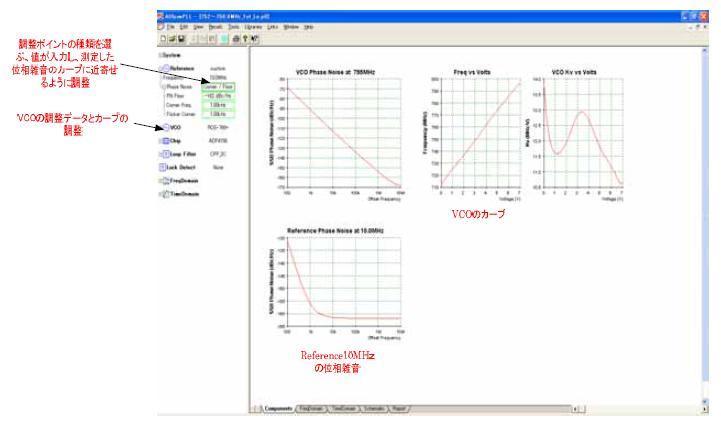

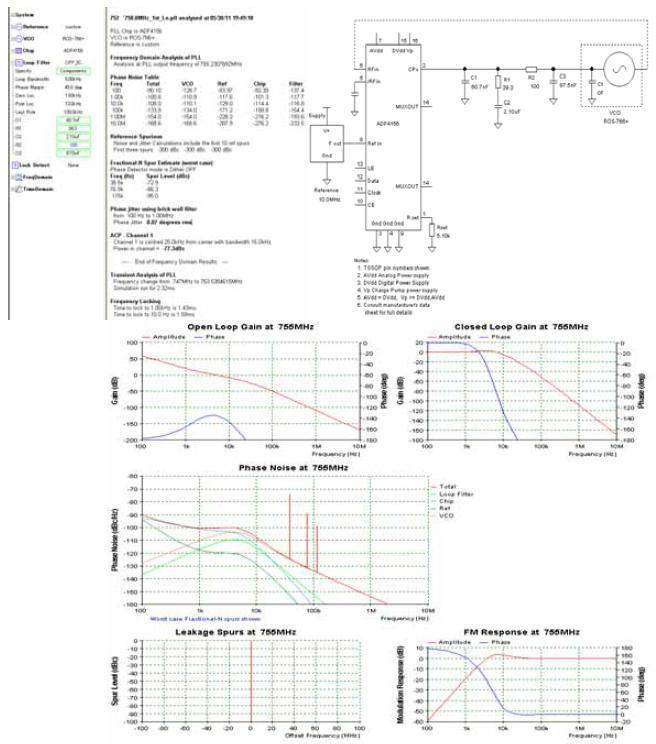

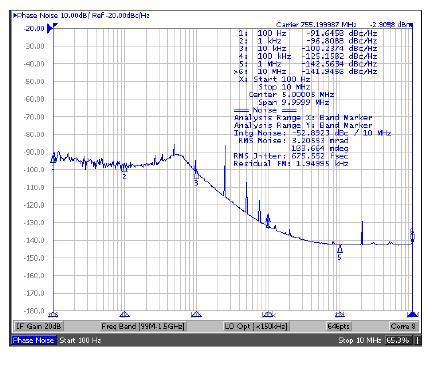

周波数シンセサイザーPLL 回路にループ・フィルターの設計は様々の要素と関係し、単にロックすればいいだけではなくて、位相雑音C/N 値から、ループ・フィルターの定数をどのように決めるかを設計例で説明します。

設計例

VCO:ROS-766+ 発振周波数:730MHz〜766MHz(Kv=12.8MHz/V)

使用PLLIC:ADF4156(REF=10MHz)

使用周波数:752MHz〜758.6MHz Step:100KHz

ループ・フィルターの定数をの算出にあたっては、PLL設計ツールADIsimPLLをダウンロードして使用しました。ループ・フィルターの定数を決める前に、使用したREF10MHzの位相雑音C/N 値を測定しておくこと。

設計手順

【1】 ADIsimPLL のSetup

Custom VCO をチェックする時、Kv の値はカタログより、TUNE SENS(MHz/V)欄から、設定する。

【2】 Reference Phase Noise の設定は、取ったREF10MHz 位相雑音C/N 値の波形によって、測定ポイントの位相雑音C/N 値に近寄せるようにCurve を調整すること。

Corner/Floor:コーナ周波数とブロードバンドの位相雑音レベル

PN Floor :dBc/Hz で表示されるブロードバンド位相雑音レベル

Corner Freq:ブロードバンド位相雑音レベルにより、レベルが3dB 高い周波数

【3】 VCO の設定について、Custom VCO をチェックする場合、カタログにより、Performance Data&Curve を調整する。

設計されたループ・フィルター

【4】 決めたループ・フィルターの定数で、VCO. 及び REF. 基準信号の 位相雑音 を与えて、Loop Bandwidth を変えて、PLL 出力の Total 位相雑音 C/N.値 の結果を シミュレーションする。このシミュレーションの結果から、Phase Margin = 45°では Loop Bandwidth 周波数 fc= 5KHzのループ・フィルターの定数:理論値と実装値(近似値)

C1 = 60.7nF = 15000pF+47000pF

R1 = 39.3Ω = 39Ω

C2 = 2.1μF = 1μF+1μF

R2 = 100Ω = 100Ω

C3 = 87.5nF = 0.1μF という値を求めることができた。

決めた定数で、設計されたPLL 回路の位相雑音C/N 値測定結果。

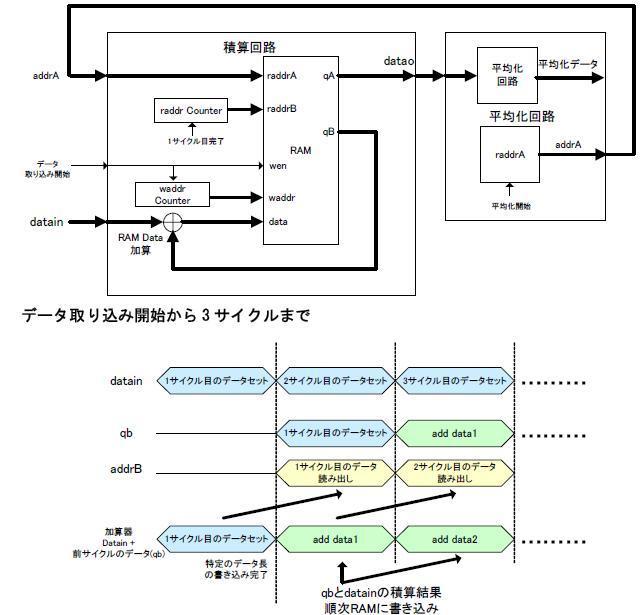

1. IP コアの概要

半導体設計におけるIP コアとはベンダから提供されている回路データ(ブロック)の事である。

2. IP コアを用いることの利点

現在の半導体設計は回路規模が膨大であり、回路の機能も多機能なものとなっている。

複雑な設計に対してIP を使用する事で設計期間の短縮が期待できる。

また、PCI Express 等の高速インターフェース、メモリブロック、DDR2 SDRAM 等のメモリコントローラ等の設計も出来る。

3. RAM IP を用いた設計例

アベレージング回路

IP によるRAM を実際に用いた設計例を記載する。下の図はアベレージング回路のブロック図である。

RAM の動作として特定のデータ長をRAM に書き込みを行う。データの書き込み完了後取り込んだデータを順次読み出し、datain と読み出しデータを積算していく。積算結果は後段の平均化回路へ読み出され、平均化回路で積算結果をアベレージングする。この回路をレジスタで作成する場合、データ長の長さの分だけシフトレジスタの段数を作成しなければならず、データ長によっては膨大なゲート数になる。RAM をもちいる事でゲート数の節約にもなる。

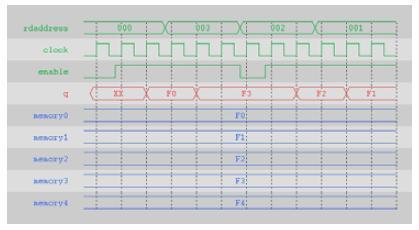

RAM IP を使用する際の設計注意点

① 読み出しタイミングについて

RAM は読み出し時に遅延が発生する。作成例に上げたアベレージング回路等にRAMを使用する場合、Clock の読み出し遅延を考慮した設計を行う必要がある。

以下の図はAltera 社のRAM を作成時に出力された読み出し時タイミングチャートである。enable の立ち上がり時、rdaddress は000 のデータを読み出しており、qからは1Clock 分の読み出し遅延が発生してF0 が出力されている。

② データの入力元と読み出し先のClock が別系統の場合

入力元、出力先のモジュールでClock が別系統の場合、Single Clock のRAM を用いた場合、正しいデータの受け渡しが出来なくなる。そのためRAM の作成時にDualClock を用いたRAM を作成し、Write Clock と、Read Clock の2 系統のClock をRAMに与えられる様にRAM IP を作成する。

③ 配線遅延

RAM を使用しFPGA 設計を行った場合、RAM は通常のゲートセルではなく、メモリブロック内で作成される。このため通常のゲートセル メモリブロック間にて配線遅延が大きくなる可能性がある。RAM のデータ出力の後段にFF を配置する事により、配線遅延によるラッチミスを防げる。

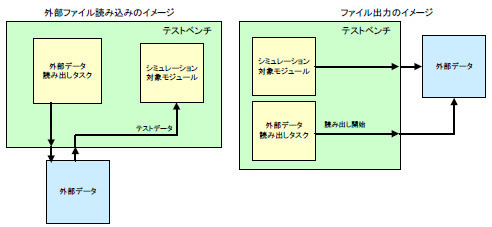

1. 概要

① Verilog-HDL のシステムタスクを用いたテストパターンの作成を行う。

② 使用するシステムタスクは『$readmemh』、『$fopen』、『$fclose』、『$fdisplay』を使用。

外部ファイルの読み込み、シミュレーションデータの外部ファイルへの書き出しを用いたシミュレーションを行う。

2. システムタスクを用いたシミュレーションについて

① 通常シミュレーションを行う場合テストベンチ上でシミュレーション対象のモジュールへ信号を与えるテスト記述を行うが、複雑なシミュレーションデータを用いてシミュレーションを行う場合、テスト記述で時間がかかり、テストソースが膨大な量になりテストソースの修正が大変である。

システムタスクを用いた場合のシミュレーションのメリットとしてテスト記述の使いまわし、記述の簡略化、検証結果のデータを外部ファイルへ出力を行う事で設計期間の短縮が期待出来る。

3. システムタスクについて

① 外部ファイルの読み出し(『$readmemh』について

『$readmemh』は16 進数データの読み出しを行うシステムタスクである。

『$readmemb』で宣言した場合2 進数データのファイルを読み出せる。

『$readmemh』宣言後(“『読み出しを行うファイル』”, 『読み出しデータの書き込みを行うレジスタの宣言』, 『先頭アドレス』, 『最終アドレス』);となっていて、読み出しを行うファイルのパスはシミュレータのプロジェクトファイルのあるディレクトリを基準としてパスを宣言する。

上記の宣言ではシミュレータのプロジェクトファイルと同じディレクトリに読み出しファイルを置く。

② 外部ファイルの書き込み(『$fopen』、『$fclose』、『$fdisplay』について)

A) 『$fopen』は書き込みを行うファイルの展開を行うシステムタスクである。

ファイル変数のmcd を用いて記述を行う。

mcd = $fopen (“書き込みを行うファイル名”);で使用する。

B) 『$fclose』は書き込みを行ったファイルを閉じるシステムタスクである。

読み出し記述の最後に記述を入れる。

C) 『$fdisplay』はファイルへのデータの書き込みを行うシステムタスクである。

$fdisplay(mcd,”HEX データ”,書き込みを行うイベント);で使用する。

下記の記述例では i がインクリメントされるごとに16 進表記のデータをファイルへ書き込みを行う。

記述例ではデータの取り込み開始に状態遷移を用いている。

シーケンス 2’h0 でデータの取り込み開始をif 文で記述しデータの取り込みを開始。

シーケンス 2’h1 ではcnt レジスタ(カウンタ)がインクリメントされるごとに『data』をmem レジスタへ格納を行う。cnt レジスタが2048 数カウントを終えたらシーケンス2’h2 へ状態遷移を行う。

シーケンス 2’h2 ではmem レジスタに格納されたデータのファイル書き込みを行っている。

データの書き込みを行う場合、メモリ(ファイル出力を行うデータの格納しているレジスタ)への書き込みの完了後にデータを読み出さないと無効なデータが出力されるため、使用例のようにステートマシンを使用するか、メモリへのデータ書き込みの完了のイベントをフラグにデータの書き込みのイベントを開始するとよい。

4. 評価

① シミュレーション対象モジュール内にて$fopen タスクを使用しRead タスクより読み出されたデータをダンプしデータが一致していることを確認する。

② シミュレーション上にて読み出したデータとシミュレーション対象のデータの波形が一致していることを確認する。

なお、ファイル読み出しを行うデータはサイン波とする。

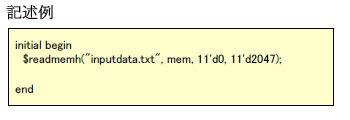

5. 回路の作成

A) 上記は読み出しファイルの先頭アドレスと最終アドレスの記述例である。

クロック同期で先頭アドレスから順次読みだされる。

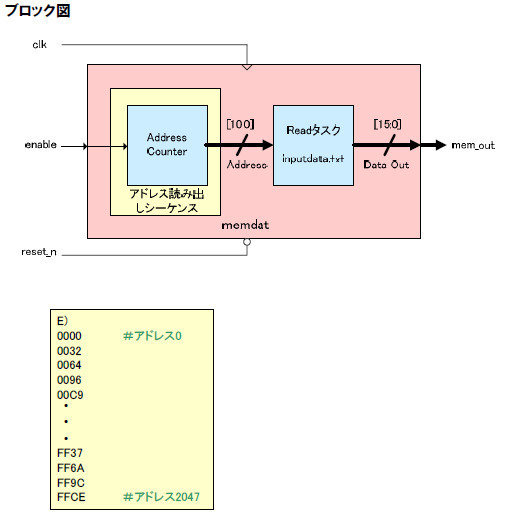

6. 結果

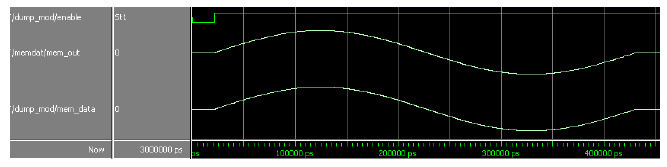

① 下図に読み出しを行ったデータと、シミュレーション対象からダンプを行ったデータの先頭アドレス付近と、最終アドレス付近のデータである。

先頭アドレス、最終アドレス付近のデータはそれぞれ一致していた。

下図は読み出しデータと、シミュレーション対象のデータをシミュレータ上にてサイン波で表示した波形である。両波形とも波形が一致していた。

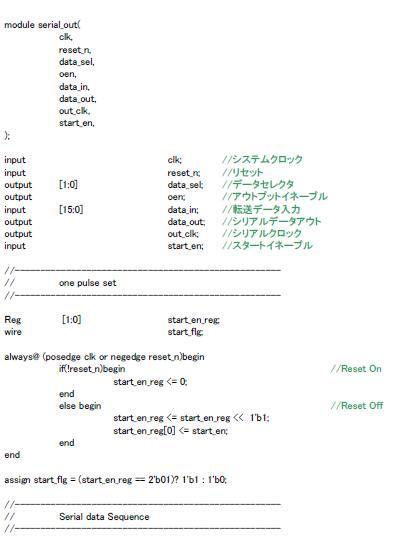

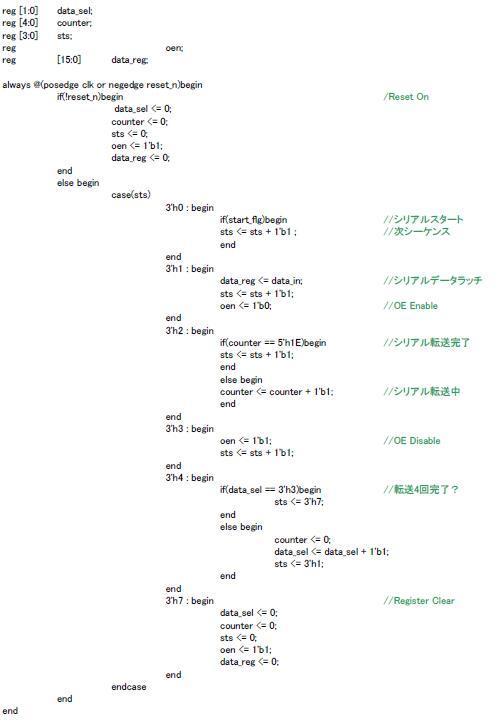

1. 概要

① Verilog-HDL によるシリアルインターフェースの作成を行う。

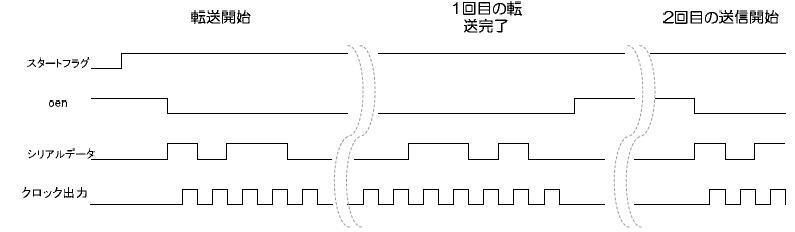

2. 動作仕様

① 送信データは16bit データ×4 セット送信を行う。

② 送信データはプリセットの他、モジュール外部から書き換え可能にする。

③ 送信タイミングは以下の通り。以下の送信を×4 セット送信を行う。

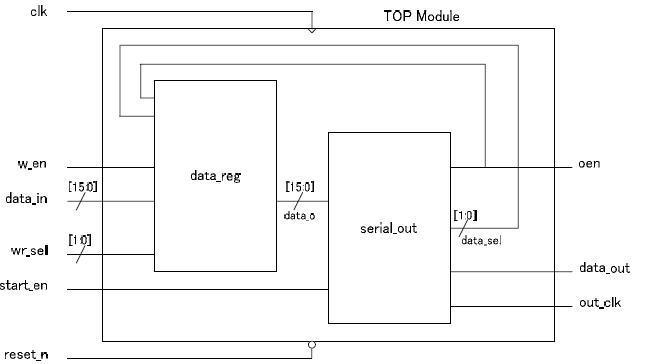

bブロック図

3. ソース記述

Data_reg ブロック

・シリアルデータの保持、書き換えを行う。

・シリアル転送回数より、次に送信するシリアルデータのセレクトを行う。

data_reg ブロックソース

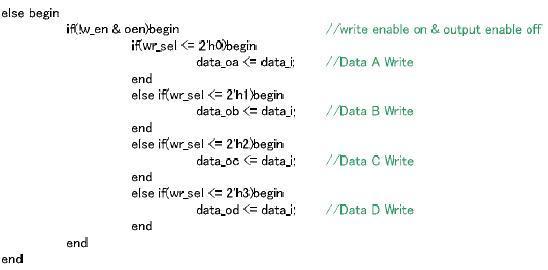

・書き換えデータセレクト

データレジスターブロックへのデータ書き込み条件は、シリアル転送を行っていない時(oen = H 時)、w_en がL 時で書き込み可。

wr_sel より何回目の転送データを書き換えるかセレクトする。

serial_out ブロック

・Start フラグを受信後動作開始。

・16bit データをMSB Fast でシリアルデータを4 回送信行う。

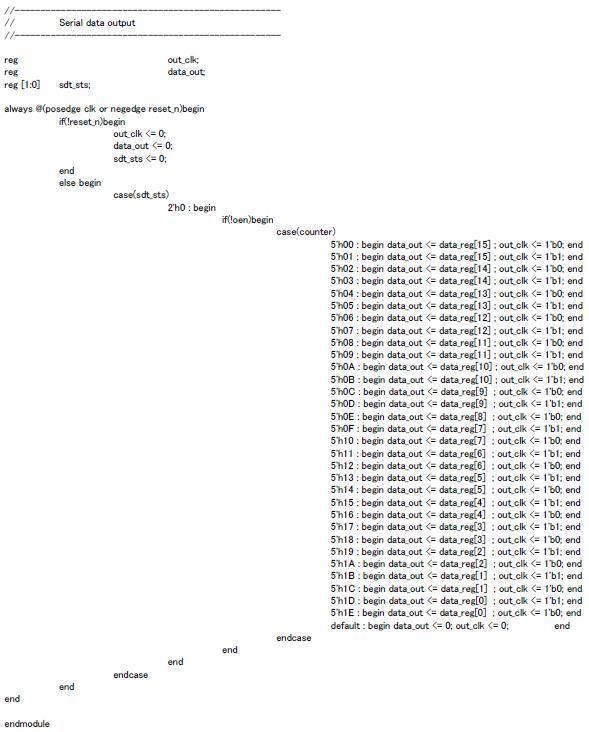

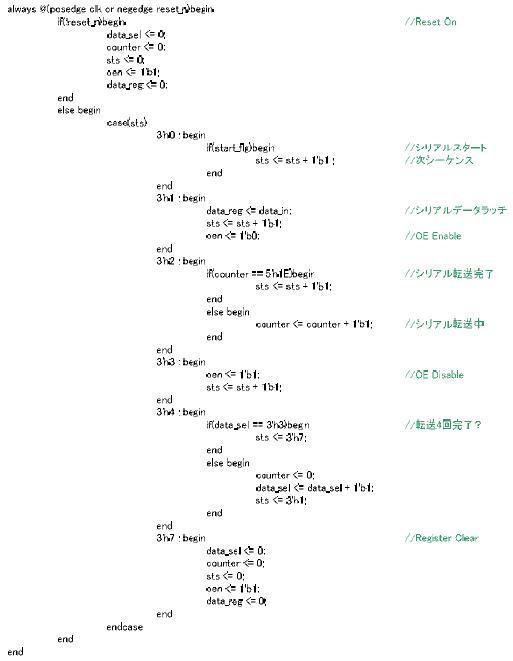

Serial_out ブロックソース

・シーケンス部ソース

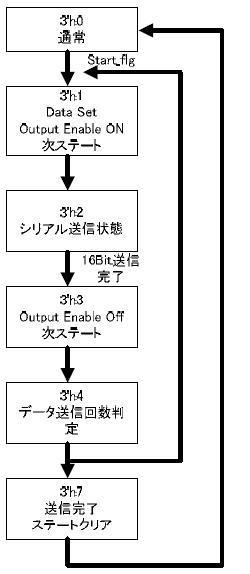

各シーケンスの状態遷移が以下の通り

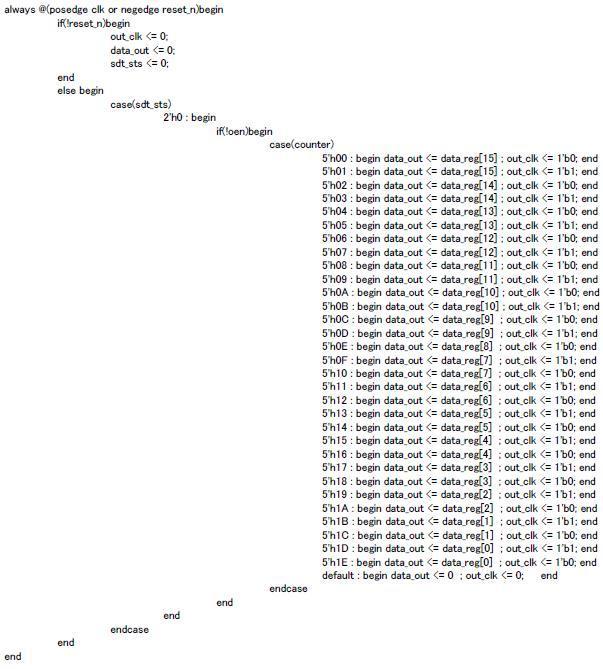

・データ送信部ソース

シリアル送信状態シーケンスに回すカウンタの値に応じて動作を行う。

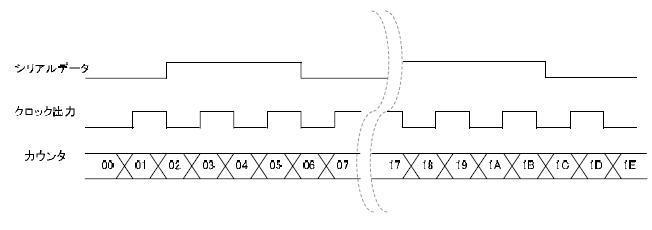

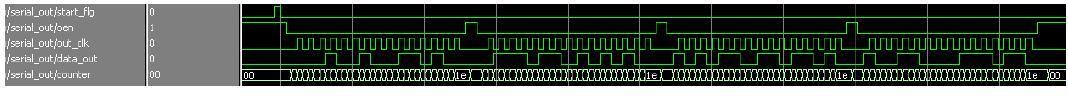

タイミングチャートは以下の通り。

4. シミュレーション

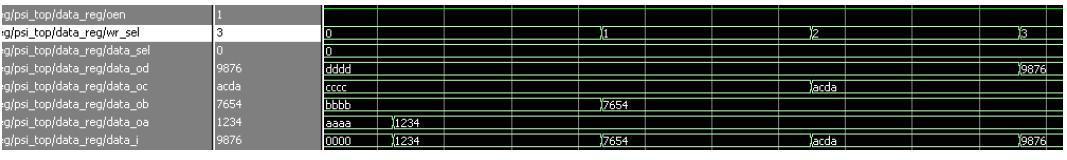

Data_reg ブロックシミュレーション

テストベンチ上からWr_sel、data_i より信号を与え、シリアルデータが書き変わること事を確認した。

・serial out ブロックシミュレーション

テストベンチ上からserial out ブロックにスタートフラグを与え、シリアルデータが送信出来ている事を確認した。

通信機器において、電気信号の周波数を変換した複数の異なる周波数の信号を一つの信号出力するため、ミキサーはよく使われています。ミキサーを使う時、データシート上でIP3(at centerband)の電気特性パラメータがあります。こちらのIP3 はIIP3 ですか、OIP3 ですかという疑問があれば、以下の様な実験で簡単に確認しよう。

ミキサーデータシートより

IP3=+18dBm、G=-7dB,LO=+14dBm

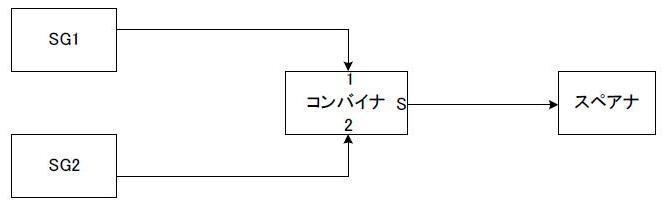

① コンバイナの出力レベルを測定する。

測定ブロック図

SG1:Freq =500MHz Power =0dBm

SG2:Freq =502MHz Power =0dBm

スペアナでコンバイナのS 側出力レベル:-1dBm

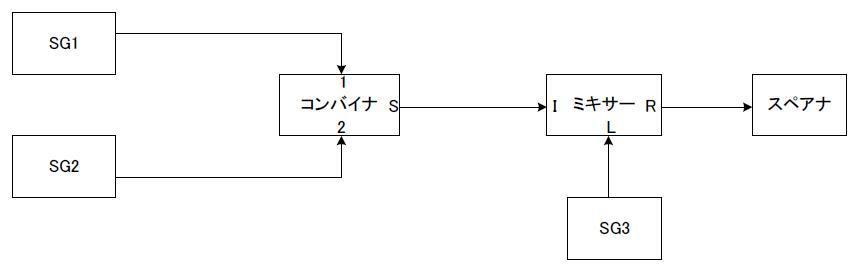

② ミキサーでRF の波形を取る。

ブロック図

ミキサーのLo に300MHz,+14dBm の信号を入力し、波形を取る。

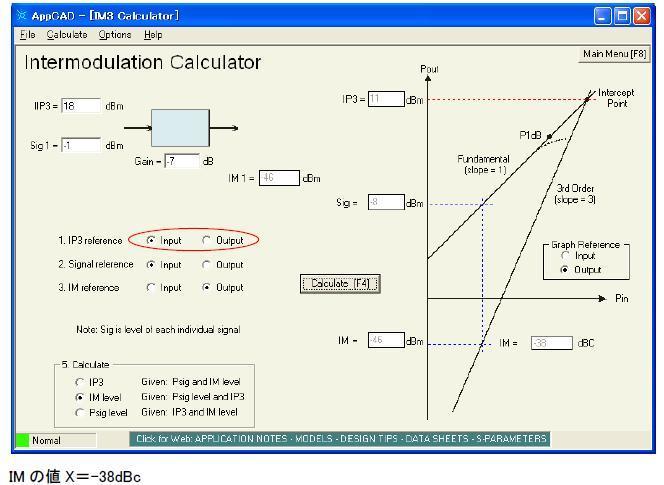

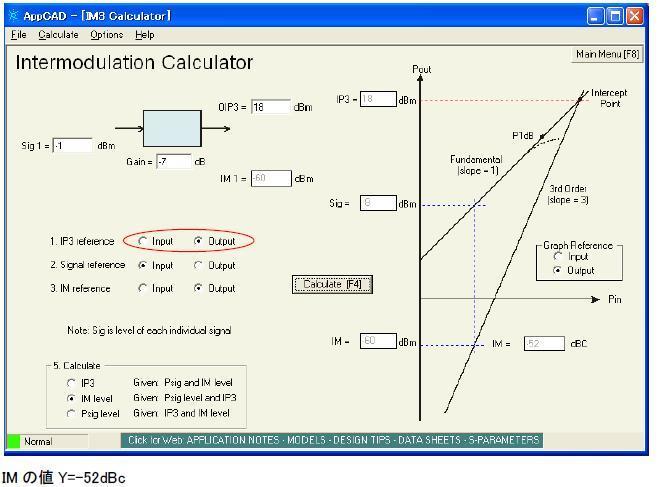

③ カタログより使われるミキサーのIP3 を調べて、AppCAD でIM を計算する。

IIP3 と仮定すると

IP3 reference ○Input ○Output 欄にInput をチェックし、IIP3,Sig1,Gain を入力して、Calculateを押す、IM の値X=-38dBc をメモしておく。

OIP3 と仮定すると

IP3 reference ○Input ○Output欄Output をチェックし、OIP3,Sig1,Gain を入力して、Calculateを押す、IM の値Y=-60dBc をメモしておく。

④ 取った波形により、IM3 の値を計算する。

取った波形によって、IM3=-44dBc

X Y とIM3 を比べて、X=-46dBc はIM3 に近寄るので、データシート上でIP3(at center band)はIIP3 となることをわかった。

信号処理分野において、フィルタは必要な信号だけ通すという働きを持って、送信機・受信機それぞれで役に立つことがあります。

<フィルタの種類>

フィルタは通過帯域ごとに低域通過フィルタ(LPF)、高域通過フィルタ(HPF)、帯域通過フィルタ(BPF)、帯域阻止フィルタ(BEF)の種類があります。

※ 通過域 : フィルタで取り出したい信号の周波数帯域

※ 減衰域 : フィルタで除去したい信号周波数帯域

各種フィルタの設計は多少異なるが、低域通過フィルタLPFを設計することができれば、他の種類のフィルタの設計はできることになると思います。

<MEL S-NAP(V5)でLPF設計仕様の説明

LPFフィルタの通過域、阻止域特性によって、MEL S-NAP/Designでは以下の特性を持っているフィルタが設計できます。

・ バターワースフィルタ

・ チェビシェフフィルタ

・ 楕円フィルタ

・ ベッセルフィルタ

① バターワースフィルタ(Butterworsh)は通過域で最大平坦な振幅特性を持つLPFです。通過域内にリップルがない特徴があります。

用途

・ 通過域にリップルを許容させない場合

② チェビシェフフィルタ(Chebyshev)は通過域で等リップルとなるようなLPFです。通過域の利得が平坦ではないので注意が必要である。リップルの大きさは設計で決めることができます。

用途

・ 通過域にリップルを許容させる場合

③ 楕円フィルタ(Elliptic)は通過域と減衰域の両方で等リップルとなるようなLPFです。

用途

・ 通過域と減衰域両側にリップルを許容させる場合

④ ベッセルフィルタ(Bessel)は通過域で遅延特性を持っているフィルタです。

<MEL S-NAP(V5)でLPF設計パラメータの説明>

チェビシェフフィルタの設計を例として、入力パラメータを説明します。

ソース/終端抵抗値 : 電源側及び負荷側の抵抗値

カットオフ周波数 fc : ある周波数よりも低い周波数を通し、高い周波数を減衰させる、この周波数カットオフ周波数(あるいは遮断周波数)と言う。その周波数を超えると信号の電力利得は通過域より3dB低下する。バンドパスフィルタを設計する時、カットオフ周波数は帯域幅以外の周波数を選択する事。

帯域内減衰量 : 通過域内のわずかな減衰量。通過域リップルRpとも言う。

減衰域参照周波数 fa : 減衰域の減衰量を指示する周波数。たとえば1.5*fc程度の周波数。

減衰域参照減衰量 Rs : 減衰域参照周波数での減衰量。

次数 : 次数は設計で決めるが、帯域内減衰量と減衰域参照減衰量によって、次数が不足する場合に自動で増やすことができるので、設計する時は小さい次数を設定しておいた方が良いです。

<設計例>

リップルRpを0.2dBにし、減衰特性が0.2dBを超え始める周波数fcを1GHzにする。また、適当な減衰域での周波数faを1.5GHzに設定して、その周波数での減衰量を30dBとする。ソース・終端インピーダンスは共に50Ωにする。

① MEL S-NAP(V5) → 【スタート】デザインを立ち上げて、LPFボタンを押す。

② LPFダイアローグに設計パラメータ入力し、設計開始。

③ 設計された回路を回路エディタにコピー、ネットリスト出力する。

④ S-NAP/Proの解析 → 単 → 解析 → 小信号 S パラメータ解析、スタート周波数とストップ周波数を設定し、解析する。

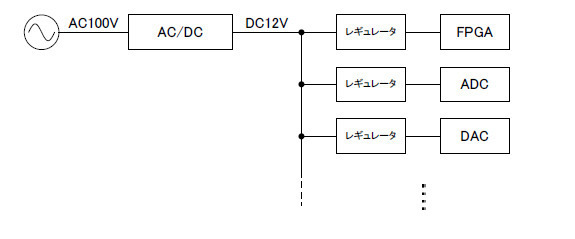

近年設計している無線システムでは、無線の信号をダウンコンバートしてADC・DACでデジタル⇔アナログ変換を行い、OFDMなどの複雑な信号処理をFPGAで行なうようになり、デジタル回路での消費電力の増大、アナログ回路でのノイズ低減が重要となっている。

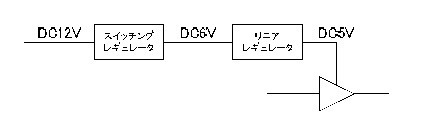

<電源構成>

各デバイスまでの電源供給は商用電源AC100VからAD/CDコンバーターで12Vを作り、レギュレーターでデバイスに合わせた電圧を作り出す構成が主流となっている。

デジタル回路では消費電流が大きいため変換効率の良いスイッチングレギュレータを使用する場合が多い。アナログ回路ではノイズを抑えたいのでリニアレギュレータを使用するが、ここで問題点の一つとしてリニアレギュレータの発熱がある。

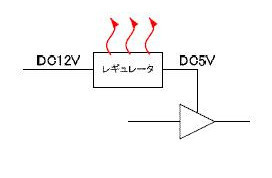

リニアレギュレータの発熱量は、おおまかに「入出力電圧差 X 消費電流」となる。アナログ回路で使用される電源電圧は3V〜5Vが多い。12Vから変換では発熱が非常に多くなり最悪の場合レギュレータが上手く動作しなくなります。解決策として巨大な放熱器を取り付ける方法がありますが無駄に電力を使うので、あまり良い方法ではありません。

そこでスイッチングレギュレータを使って6Vに変換、その後リニアレギュレータで5Vなどに変換するとリニアレギュレータの発熱量を抑えることができる。

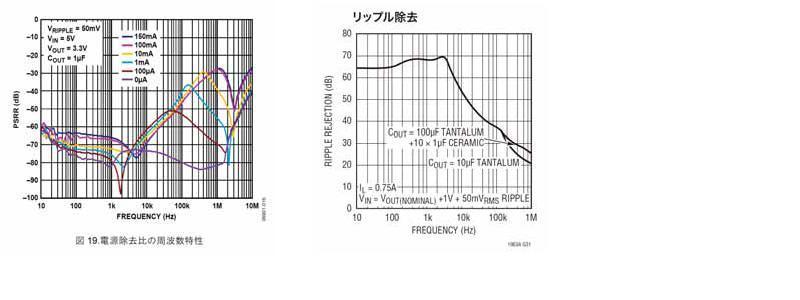

しかし、この場合ではスイッチングレギュレータでリップルノイズが発生してしまう。

この問題の対策として以下の項目を組み合わせて行なうと良い。

① LCノイズフィルタを入れる

② リップルノイズの少ないスイッチングレギュレータを使う

③ リップル除去比の高いリニアレギュレータを使う

ローノイズを謳うリニアレギュレータにはノイズ除去の周波数特性が記載されている。

例)

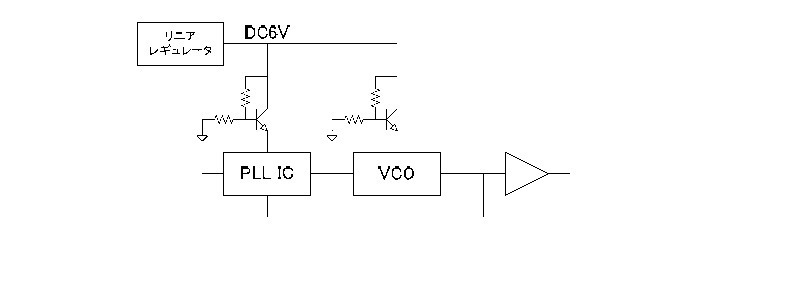

PLLの電源では、よりローノイズが求められるためリニアレギュレータの後にトランジスタバイアス回路を入れて更にノイズ除去を行う。

<アナログ・デジタル混在基板>

ADCやDACを使用する基板ではアナログ回路とデジタル回路が必ず混在することになる。以下の注意点が有る。

① 部品の配置はアナログとデジタルが、はっきりと分かれるようにする。

アナログ回路の部分にシールドケースを取り付けるためにシンプルな長方形の確保や、デジタル回路の配線を遠ざけるため。

② 内層の電源配線もアナログとデジタルを分けておく。

基板設計を外注した場合の検図で注意しておかないと、電源がベタ配線になってアナログ回路の部分にまで配線が入り込んでいる場合があるため。

③ 電源の供給元(12Vなど)のコネクタは消費電力の大きいデジタル側に配置する。

パターンの抵抗により電圧降下が起こるため、電流の多い部分への電源配線をなるべく短くするため。

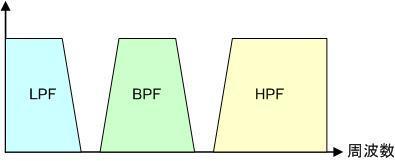

フィルタの種類

フィルタは通過帯域ごとに大きく分けると以下の3つがある

・ ローパスフィルタ(LPF)

低い帯域の周波数を通過させ、帯域以上の周波数のカットを行うフィルタ

・ バンドパスフィルタ(BPF)

特定の帯域の周波数を通過させ、帯域外の周波数のカットを行うフィルタ

・ ハイパスフィルタ(HPF)

高い帯域の周波数を通過させ、帯域以下の周波数のカットを行うフィルタ

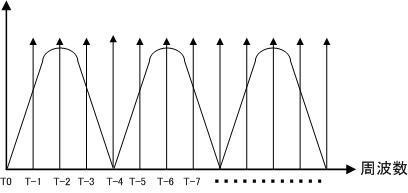

(以下の図参照)

図1

デジタルフィルタの種類

デジタルフィルタには大きく分けてFIRフィルタとIIRフィルタの2つがある

・ FIRフィルタ

有限インパルス応答フィルタの略

入力データの決められた時間内のサンプリングデータを用いて演算を行う

決められた時間より経過したサンプリングデータの演算は行わない

・ IIRフィルタ

無限インパルス応答フィルタの略

一度入力されたサンプリングデータの演算を無限に使用する

欠点として、サンプリングデータに異常がある場合、過去のデータを永久的に演算するため

出力データが不安定になる

サンプリング周波数は入力される周波数の1/2以下の周波数でサンプリングを行う

図2

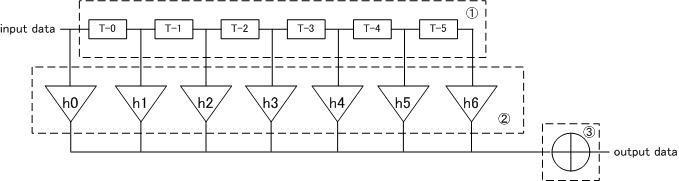

デジタルフィルタの構成

デジタルフィルタ(FIR)は遅延素子、乗算器、加算器より構成されている

図3

計算式

output = input data × h0 + T-0 × h1 + T-1 × h2 + T-1 × h2 + T-2 × h3 + T-3 × h4 + T-4 × h5 + T-5 × h6

(構成されているTAP数に応じて乗算数が増減する)

①遅延素子

入力データに対しT分の遅延を行う。1遅延素子分が1サンプリング分の遅延に相当

※ 図2参照

②乗算器

各サンプリングを行ったデータに対し、カットオフを行う周波数の係数の乗算を行う

各hのパラメータの重みを変える事で通過帯域の特性を設定する

③加算器

①、②の各乗算結果の加算を行う

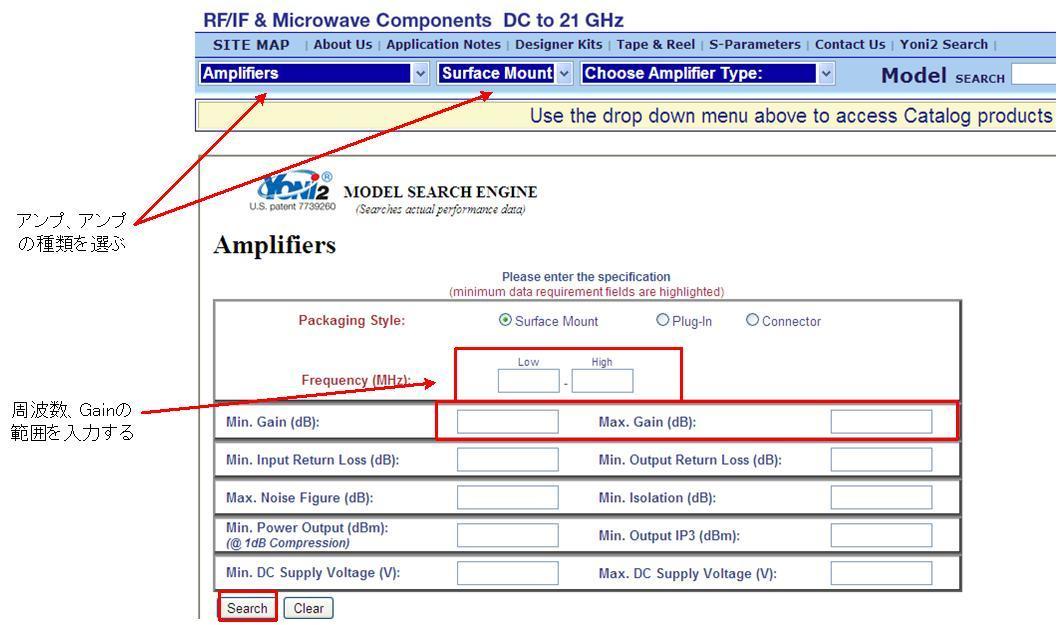

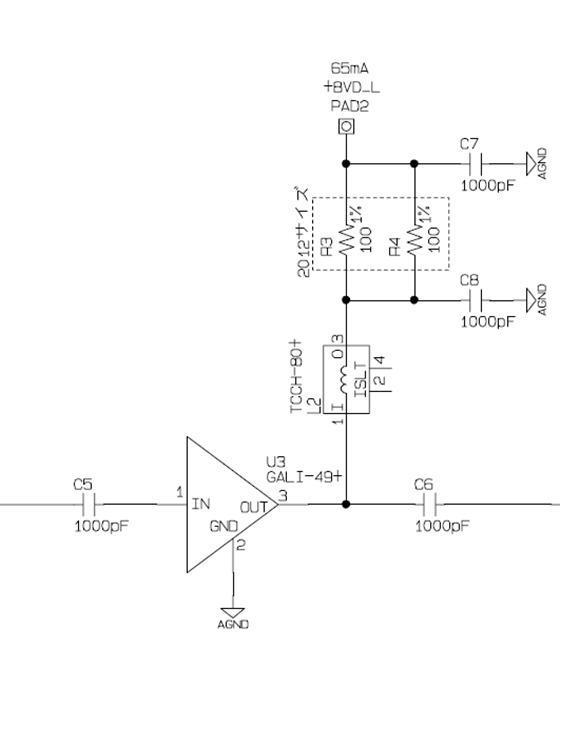

増幅回路を扱う信号の周波数、利得によってアンプを選ぶ。

Mini-Circuits のGALIシリーズアンプを例として、簡単に説明します。

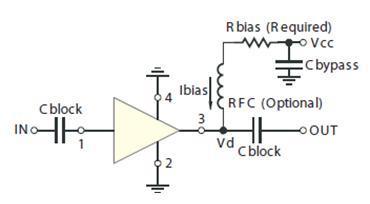

アンプGALI****定数

アンプの出力付近の電気信号が入力に帰還することで発振する可能性がある。

増幅回路の出力の変化に伴う消費電流の変化が電圧降下として現われ、増幅回路の素子に

影響を与えて発振することがある。これを防ぐために、電源回路内に低抵抗やチョークコイルを

接続し、その前後を大容量のコンデンサを通して接地する。これにより、消費電流の変化に

伴う電圧降下が別の増幅素子に伝わることが少なくなる。

データシートにより、

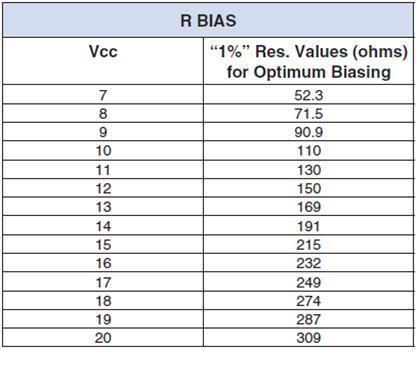

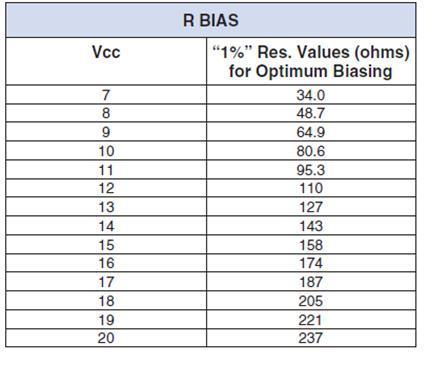

① Rbias

アンプの品番によって、データシートに R BIAS の規定値は異なる。

Vcc (一般的に Vcc は8V)の電圧値により、R bias の値を選ぶ。

② Ibias

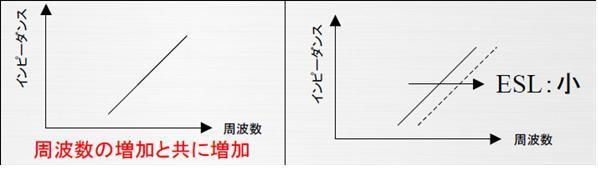

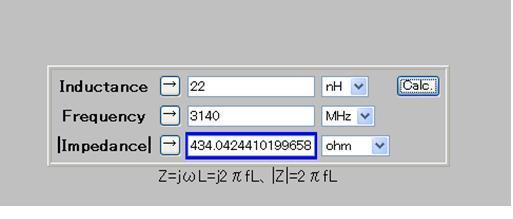

コイルのインピーダンスと周波数の関係 :

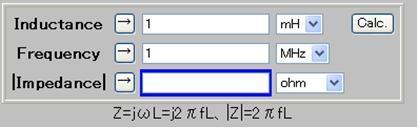

扱う信号の周波数を入力して、Inductance を調整しながら、l Impedance l の値は

100ohm〜1000ohm の範囲に入れば、コイルのインダクタンスを決める。

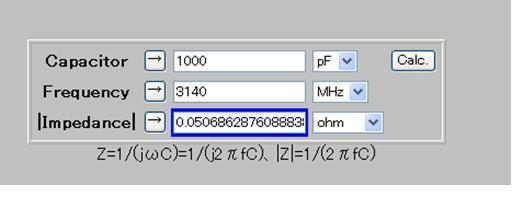

③ Cblock

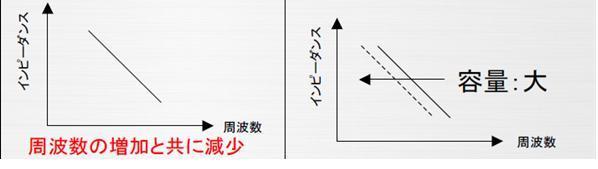

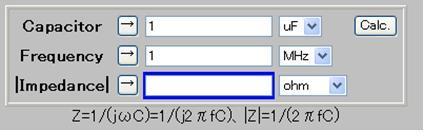

コンデンサのインピーダンスと周波数の関係 :

扱う信号の周波数を入力して、Capacitor を調整しながら、l Impedance l の値は

1ohm以下の範囲に入れば、コンデンサのキャパシタンスを決める。

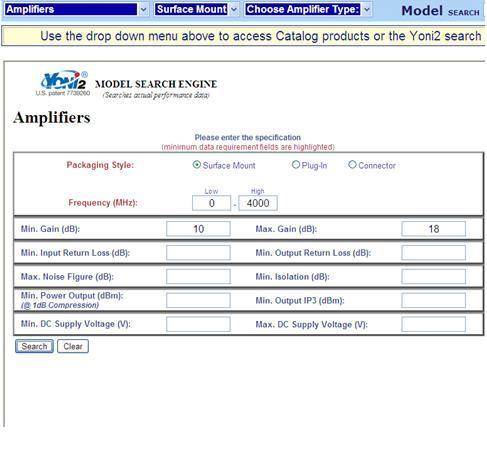

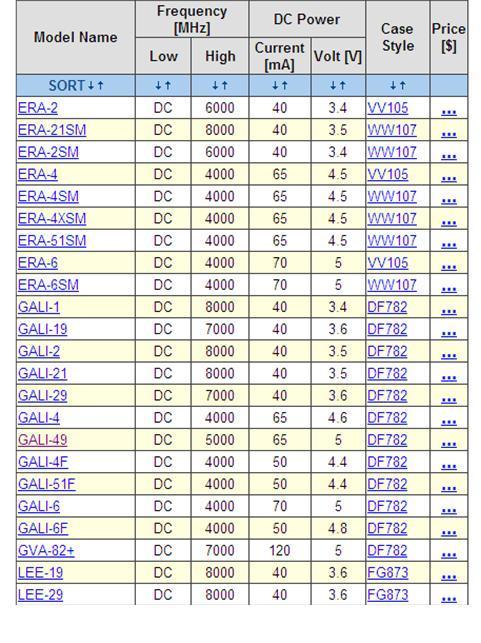

1.アンプ品番を決める

周波数、Mini Gain、Max Gain の欄に数値を入力し、Search ボタンを押せば、

次画面が出てくる。

任意品番のアンプのデータシートを開けてみて、周波数と Gain が当たるかを確認する

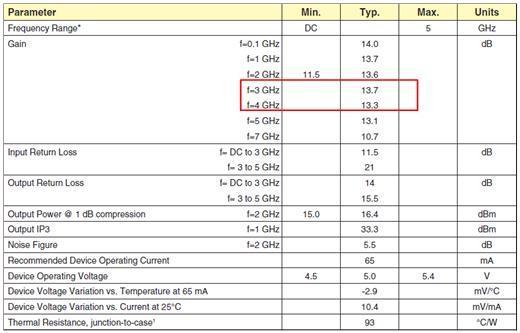

GALI-49+ を選ぶことになった

2.定数を決める

① Rbias

GALI-49+のデータシートにより、

Vcc 8V の場合、Rbias は48.7Ωです。抵抗の系列によって、Rbias は50Ωを選ぶ

② Ibias

l Impedance l の値は 100ohm~1000ohm の範囲に入る事がわかる

③ Cblock

|Impedance|の値は1ohm以下の範囲に入る。Cblock=1000pFを決める。

定数を決めた回路図

お問合せ・ご相談はこちら

弊社はアナログおよびデジタルの電子回路設計でお悩みのお客様に、最適なハードウエアデザイン・ソフトウエアデザインをご提供します。

高周波アナログ回路設計と高集積ロジック信号処理の両方に強みを持っております。

また、環境に配慮した省電力、省資源で電子機器のシステム化をお手伝いします。

アナログデジタル電子回路設計センター

住所

〒224-0041

神奈川県横浜市都筑区仲町台1-3-7

アクセス

◆電車でお越しの場合

横浜市営地下鉄ブルーライン 仲町台駅より徒歩1分

◆お車でお越しの場合

第三京浜 都筑インターより5分