〒224-0041 神奈川県横浜市都筑区仲町台1-3-7

◆電車でお越しの場合

横浜市営地下鉄ブルーライン 仲町台駅より徒歩1分

◆お車でお越しの場合

第三京浜 都筑インターより5分

周波数シンセサイザーPLL 回路にループ・フィルターの設計は様々の要素と関係し、単にロックすればいいだけではなくて、位相雑音C/N 値から、ループ・フィルターの定数をどのように決めるかを設計例で説明します。

設計例

VCO:ROS-766+ 発振周波数:730MHz〜766MHz(Kv=12.8MHz/V)

使用PLLIC:ADF4156(REF=10MHz)

使用周波数:752MHz〜758.6MHz Step:100KHz

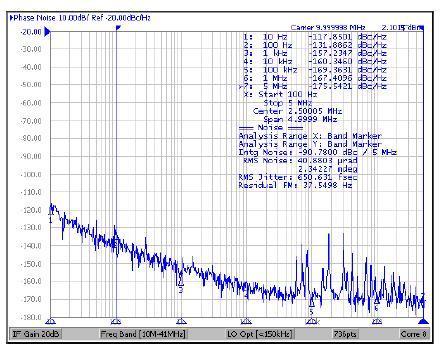

ループ・フィルターの定数をの算出にあたっては、PLL設計ツールADIsimPLLをダウンロードして使用しました。ループ・フィルターの定数を決める前に、使用したREF10MHzの位相雑音C/N 値を測定しておくこと。

設計手順

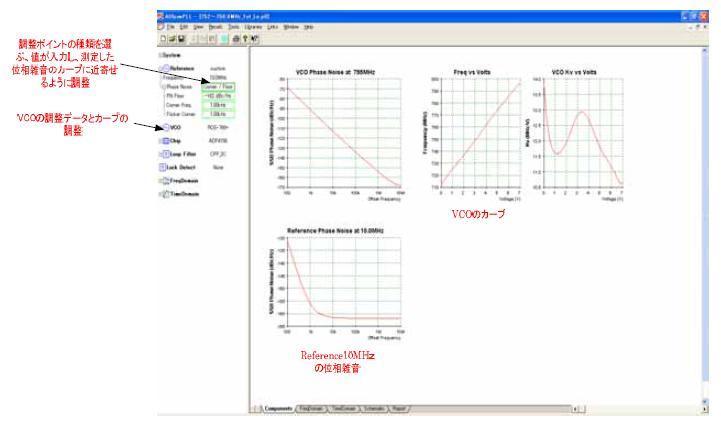

【1】 ADIsimPLL のSetup

Custom VCO をチェックする時、Kv の値はカタログより、TUNE SENS(MHz/V)欄から、設定する。

【2】 Reference Phase Noise の設定は、取ったREF10MHz 位相雑音C/N 値の波形によって、測定ポイントの位相雑音C/N 値に近寄せるようにCurve を調整すること。

Corner/Floor:コーナ周波数とブロードバンドの位相雑音レベル

PN Floor :dBc/Hz で表示されるブロードバンド位相雑音レベル

Corner Freq:ブロードバンド位相雑音レベルにより、レベルが3dB 高い周波数

【3】 VCO の設定について、Custom VCO をチェックする場合、カタログにより、Performance Data&Curve を調整する。

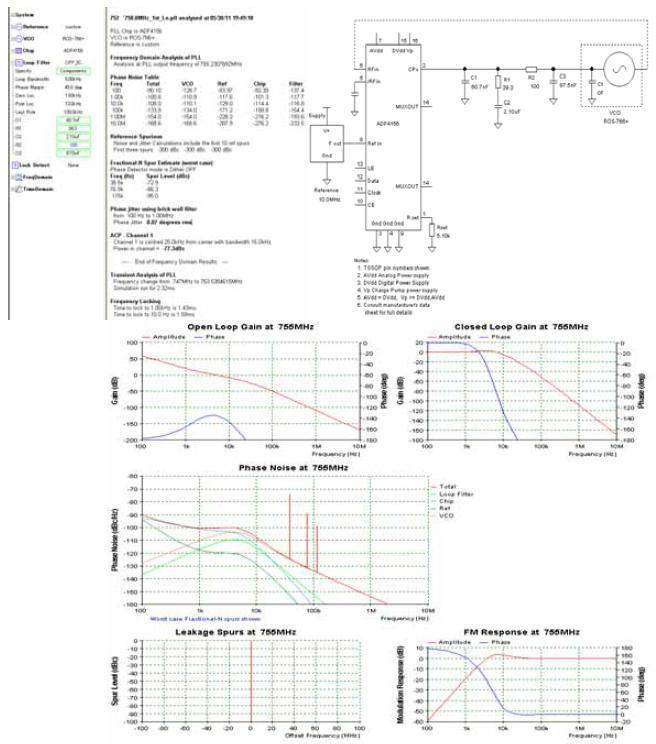

設計されたループ・フィルター

【4】 決めたループ・フィルターの定数で、VCO. 及び REF. 基準信号の 位相雑音 を与えて、Loop Bandwidth を変えて、PLL 出力の Total 位相雑音 C/N.値 の結果を シミュレーションする。このシミュレーションの結果から、Phase Margin = 45°では Loop Bandwidth 周波数 fc= 5KHzのループ・フィルターの定数:理論値と実装値(近似値)

C1 = 60.7nF = 15000pF+47000pF

R1 = 39.3Ω = 39Ω

C2 = 2.1μF = 1μF+1μF

R2 = 100Ω = 100Ω

C3 = 87.5nF = 0.1μF という値を求めることができた。

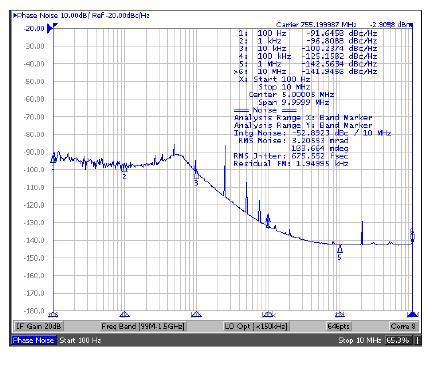

決めた定数で、設計されたPLL 回路の位相雑音C/N 値測定結果。

お問合せ・ご相談はこちら

弊社はアナログおよびデジタルの電子回路設計でお悩みのお客様に、最適なハードウエアデザイン・ソフトウエアデザインをご提供します。

高周波アナログ回路設計と高集積ロジック信号処理の両方に強みを持っております。

また、環境に配慮した省電力、省資源で電子機器のシステム化をお手伝いします。

アナログデジタル電子回路設計センター

住所

〒224-0041

神奈川県横浜市都筑区仲町台1-3-7

アクセス

◆電車でお越しの場合

横浜市営地下鉄ブルーライン 仲町台駅より徒歩1分

◆お車でお越しの場合

第三京浜 都筑インターより5分