〒224-0041 神奈川県横浜市都筑区仲町台1-3-7

◆電車でお越しの場合

横浜市営地下鉄ブルーライン 仲町台駅より徒歩1分

◆お車でお越しの場合

第三京浜 都筑インターより5分

1. IP コアの概要

半導体設計におけるIP コアとはベンダから提供されている回路データ(ブロック)の事である。

2. IP コアを用いることの利点

現在の半導体設計は回路規模が膨大であり、回路の機能も多機能なものとなっている。

複雑な設計に対してIP を使用する事で設計期間の短縮が期待できる。

また、PCI Express 等の高速インターフェース、メモリブロック、DDR2 SDRAM 等のメモリコントローラ等の設計も出来る。

3. RAM IP を用いた設計例

アベレージング回路

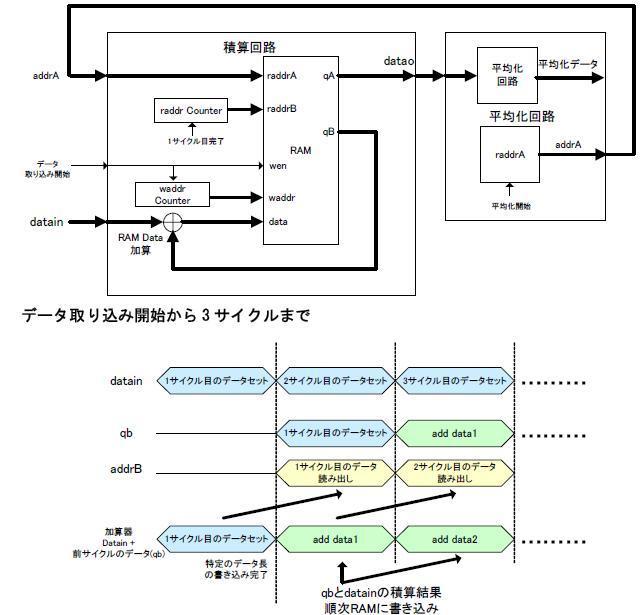

IP によるRAM を実際に用いた設計例を記載する。下の図はアベレージング回路のブロック図である。

RAM の動作として特定のデータ長をRAM に書き込みを行う。データの書き込み完了後取り込んだデータを順次読み出し、datain と読み出しデータを積算していく。積算結果は後段の平均化回路へ読み出され、平均化回路で積算結果をアベレージングする。この回路をレジスタで作成する場合、データ長の長さの分だけシフトレジスタの段数を作成しなければならず、データ長によっては膨大なゲート数になる。RAM をもちいる事でゲート数の節約にもなる。

RAM IP を使用する際の設計注意点

① 読み出しタイミングについて

RAM は読み出し時に遅延が発生する。作成例に上げたアベレージング回路等にRAMを使用する場合、Clock の読み出し遅延を考慮した設計を行う必要がある。

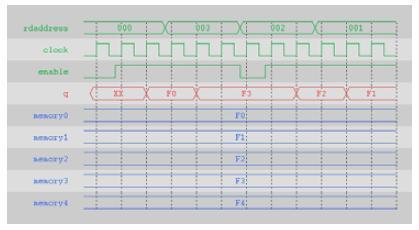

以下の図はAltera 社のRAM を作成時に出力された読み出し時タイミングチャートである。enable の立ち上がり時、rdaddress は000 のデータを読み出しており、qからは1Clock 分の読み出し遅延が発生してF0 が出力されている。

② データの入力元と読み出し先のClock が別系統の場合

入力元、出力先のモジュールでClock が別系統の場合、Single Clock のRAM を用いた場合、正しいデータの受け渡しが出来なくなる。そのためRAM の作成時にDualClock を用いたRAM を作成し、Write Clock と、Read Clock の2 系統のClock をRAMに与えられる様にRAM IP を作成する。

③ 配線遅延

RAM を使用しFPGA 設計を行った場合、RAM は通常のゲートセルではなく、メモリブロック内で作成される。このため通常のゲートセル メモリブロック間にて配線遅延が大きくなる可能性がある。RAM のデータ出力の後段にFF を配置する事により、配線遅延によるラッチミスを防げる。

お問合せ・ご相談はこちら

弊社はアナログおよびデジタルの電子回路設計でお悩みのお客様に、最適なハードウエアデザイン・ソフトウエアデザインをご提供します。

高周波アナログ回路設計と高集積ロジック信号処理の両方に強みを持っております。

また、環境に配慮した省電力、省資源で電子機器のシステム化をお手伝いします。

アナログデジタル電子回路設計センター

住所

〒224-0041

神奈川県横浜市都筑区仲町台1-3-7

アクセス

◆電車でお越しの場合

横浜市営地下鉄ブルーライン 仲町台駅より徒歩1分

◆お車でお越しの場合

第三京浜 都筑インターより5分